发布日期:2016-02-29 来源:中声文

AD9278针对低成本、低功耗、小尺寸及易于使用的应用而设计。它内置八通道的可变增益放大器(VGA)、低噪声前置放大器(LNA)、抗混叠滤波器(AAF)、12位10 MSPS至65 MSPS模数转换器(ADC)以及具有可编程相位旋转的I/Q解调器。

每个通道均具有45 dB的可变增益范围、完全差分信号路径、有源输入前置放大器终端、最大51 dB的增益以及转换速率高达65 MSPS的ADC。通道专门针对动态范围与低功耗而优化,适合要求小封装尺寸的应用。

LNA具有单端转差分增益,可以通过SPI进行选择。增益为21.3 dB时,LNA输入噪声典型值为1.3 nV/¡ÌHz;在最大增益下,所有通道的折合到输入端噪声为1.3 nV/¡ÌHz。假设噪声带宽为15 MHz且LNA增益为21.3 dB,则输入信噪比(SNR)约为88 dB。在CW多普勒模式下,各LNA输出驱动一个I/Q解调器。各解调器具有16种相位设置,可以通过SPI实现独立可编程相位旋转。

AD9278要求采用LVPECL/CMOS/LVDS兼容型采样速率时钟信号,以便充分发挥其工作性能。对于大多数应用来说,无需外部基准电压源或驱动器件。

为获得合适的LVDS串行数据速率,该ADC会自动倍乘采样速率时钟。它提供一个数据时钟(DCO±)用于在输出端捕获数据,以及一个帧时钟(FCO±)触发器用于发送新输出字节信号。

各通道可单独进入掉电模式,从而延长便携式应用的电池使用时间。利用待机模式选项可以快速上电,以便开机重启。以CW多普勒模式工作时,VGA、AAF和ADC均进入掉电模式。TGC路径的功耗与可选ADC速度功耗模式成正比。

ADC内置多种功能特性,例如可编程时钟、数据对准、生成可编程数字测试码等,可使器件的灵活性达到最佳、系统成本降至最低。数字测试码包括内置的固定码和伪随机码,以及通过串行端口接口输入的用户自定义测试码。

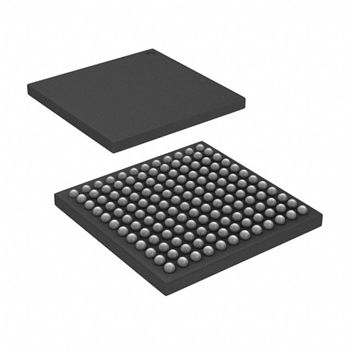

AD9278采用先进的BiCMOS工艺制造,提供10 mm × 10 mm、符合RoHS标准的144引脚BGA封装,额定温度范围为−40°C至+85°C工业温度范围。

优势和特点

低功耗:TGC模式下每通道88 mW,40 MSPS;

CW模式下每通道32 mW

10 mm × 10 mm、144引脚CSP-BGA封装

TGC 通道折合到输入端噪声:1.3 nV/√Hz(最大增益)

灵活的省电模式

可从低功耗待机模式快速恢复:<2 μs

过载恢复:<10 ns

折合到输入端噪声:1.25 nV/√Hz(增益 = 21.3 dB)

可编程增益:15.6 dB/17.9 dB/21.3 dB

0.1 dB 压缩:1000 mV p-p/750 mV p-p/450 mV p-p

双模式有源输入阻抗匹配

带宽(BW):> 50 MHz

衰减器范围:−45 dB至0 dB

后置放大器增益(PGA):21 dB/24 dB/27 dB/30 dB

线性dB增益控制

可编程二阶LPF范围:8 MHz至18 MHz

可编程HPF

信噪比(SNR):70 dB(12位,最高65 MSPS)

串行LVDS(ANSI-644,低功耗/减少信号)

独立可编程相位旋转

每通道输出动态范围:>158 dBc/√Hz

折合到输出端SNR:153 dBc/√Hz(1 kHz偏移,−3dBFS)